■マルチビットD/Aコンバータをノイズシェーパーでドライブ

◆2016/09/14 実験の概要

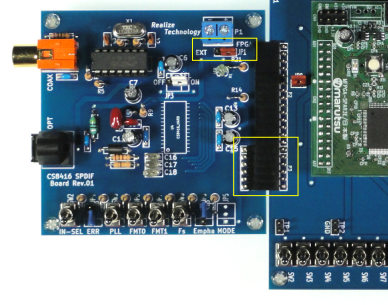

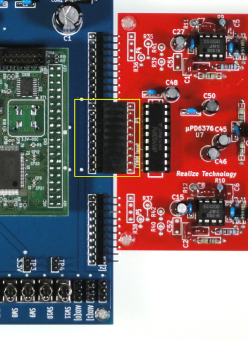

SPDIFボード:RTD-CS8416_MP01・ΔΣ方式と呼ばれるノイズシェーピングによるD/Aコンバータでは、PWM出力にすることでフルロジックでの構成が可能で す。 ・性能を向上させるには、ノイズシェーパーの次数を上げる、PWMのValue数を増加させる等が上げられますが、クロック Jitterによる性能の劣化、ノイズシェーパーの高次化や高速クロックによる後段のフィルタの負荷増大などが発生します。 ・またノイズシェーピング方式のD/Aでは、パターンノイズによるアイドルトーンの発生が知られています。 ・これらのバックグラウンドから、ノイズシェーパー+マルチビットD/Aコンバータの実験を行ってみる事にしました。 FPGAボード:RTD-XC3S250E_MP01 D/Aコンバータボード:RTA-μPD6376_MP01 ・これらのボードを使用して、デジタルオーディオ信号にノイズシェーピングを施し、マルチビット方式のD/Aコンバータを ドライブしてみます。 まず、D/Aコンバータボードに搭載してあるマルチビット(抵抗ストリング)方式のD/AコンバータIC μPD6376の 電気的特性を掲載します。  ◆2016/09/15 D/Aコンバータボード:RTA-μPD6376_MP01の特性測定 SPDIFボード(RTD-CS8416_MP01)とFPGAボード(RTD-XC3S250E_MP01)との接続 ⇒SPDIFボードのP3(6pin)とFPGAボードのP3(6pin)を接続し、SPDIFボードのJP1をFPGA側にセット  FPGAボード(RTD-XC3S250E_MP01)とD/Aボード(RTA-μPD6376_MP01)との接続

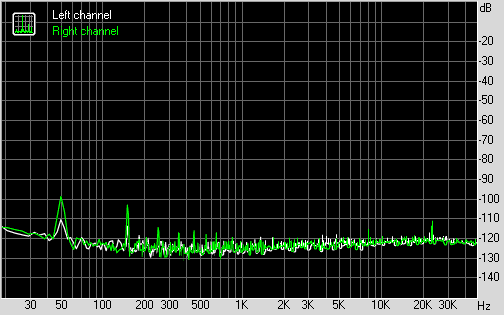

⇒FPGAボードのP7(10pin)とD/AボードのP3(10pin)を接続  ・測定時に使用したFPGAのROMデータ ダウンロードはこちら (SPDIFからデジタルデータを入力し、D/Aコンバータボードのフォーマットで出力するフォーマットコンバータ) ・FPGAボードの信号とSW設定は以下の通り SW10とSW11の組み合わせで、SPDIFからの入力信号フォーマットを変更する事ができます。 SW10/SW11:L / L 通常フォーマット24bit左詰め SW10/SW11:L / H I2Sフォーマット SW10/SW11:H / L 通常フォーマット24bit右詰め  RMAAによる測定結果 ・D/AコンバータICの出力を測定 RightMark Audio Analyzer test report

Summary

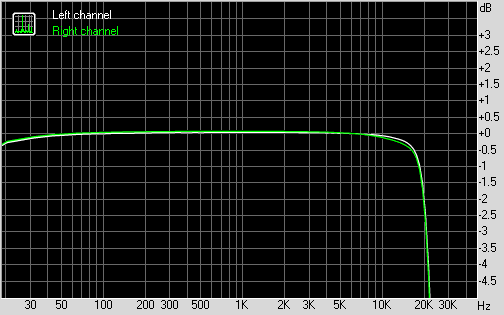

Frequency response

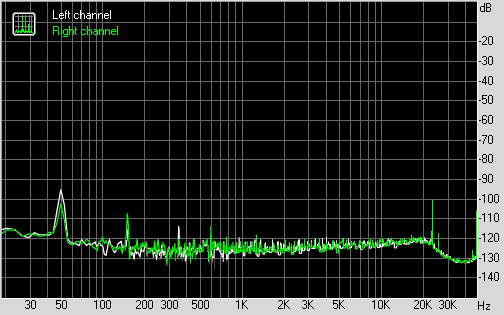

Noise level

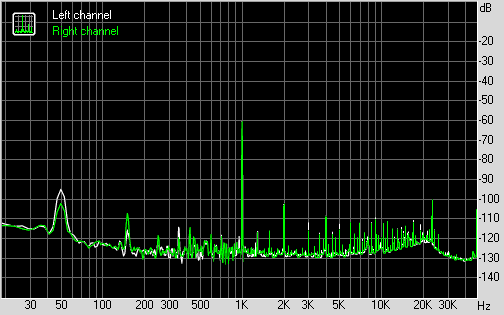

Dynamic range

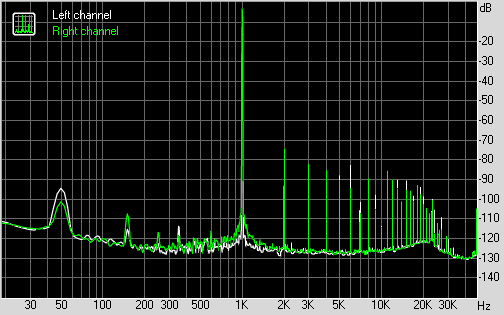

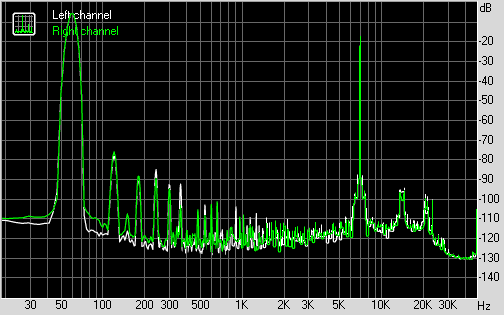

THD + Noise (at -3 dB FS)

Intermodulation distortion

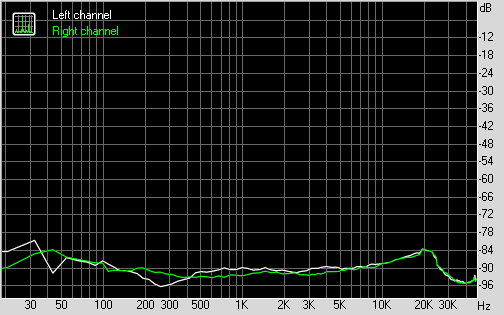

Stereo crosstalk

IMD (swept tones)

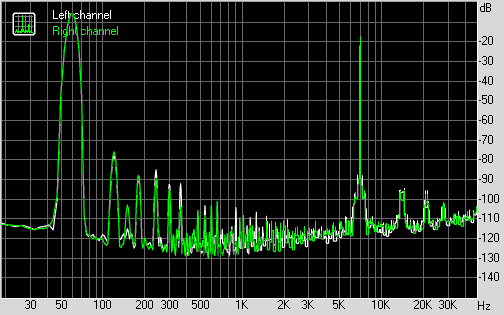

・D/Aコンバータボード(RTA-μPD6376_MP01)の出力を測定 RightMark Audio Analyzer test report

Summary

Frequency response

Noise level

Dynamic range

THD + Noise (at -3 dB FS)

Intermodulation distortion

Stereo crosstalk

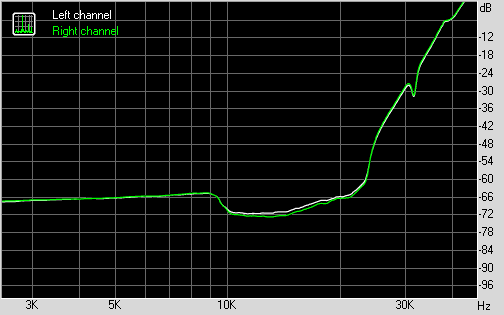

IMD (swept tones)

|

| | プライバシーポリシー | 特定商取引法に基づく表示 | 営業日カレンダー | 送料 | お問い合せ | 会社概要 | Copyright (C) 2015-2020 Realize Technology Corporation All Rights Reserved. |