üĪā}āŗā`ārābāgD/AāRāōāoü[ā^éāmāCāYāVāFü[āpü[é┼āhāēāCāuüiéQüj

ü¤2016/09/20ü@āóā░ī^āmāCāYāVāFü[āpü[é┼é╠ō«Źņō┴ɽ

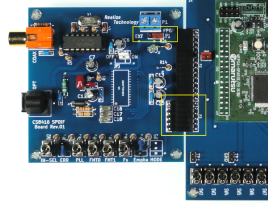

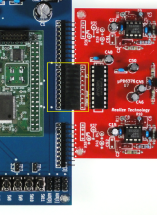

ü@üEé▒é▒é▄é┼é═üAÆ╩ÅĒé╠PCMāfü[ā^éÆ╝É┌ō³Ś═éĄéĮÅĻŹćé╠D/AāRāōāoü[ā^ā{ü[āhé╠ō┴ɽéīfŹ┌éĄé─é½é▄éĄéĮüB ü@ü@üi2016/09/15é╠ō┴ɽāfü[ā^üj ü@üEŹĪē±é═éóéµéóéµ¢{æĶé╠üAāmāCāYāVāFü[āpü[é┼ā}āŗā`ārābāgD/AāRāōāoü[ā^éō«Źņé│é╣éĮÅĻŹćé╠ō┴ɽéīfŹ┌éĄé▄éĘüB ü@ü@āmāCāYāVāFü[āpü[ü@ĤÉöüF1Ĥü`7ĤüAValueÉöüF5bitü`12bit ü@üEā{ü[āhé╠É┌æ▒é═æOē±éŲō»éČé┼éĘüBüił╚ē║é╠Æ╩éĶüjü@ ü@ü@ć@SPDIFā{ü[āhüiRTD-CS8416_MP01)éŲFPGAā{ü[āhüiRTD-XC3S250E_MP01)éŲé╠É┌æ▒ ü@ü@ü@SPDIFā{ü[āhé╠P3üi6pinüjéŲFPGAā{ü[āhé╠P3üi6pin)éÉ┌æ▒éĄüASPDIFā{ü[āhé╠JP1éFPGAæżé╔āZābāg ü@ü@ćAFPGAā{ü[āhüiRTD-XC3S250E_MP01)éŲD/Aā{ü[āhüiRTA-ā╩PD6376_MP01)éŲé╠É┌æ▒

ü@ü@ü@FPGAā{ü[āhé╠P7üi10pinüjéŲD/Aā{ü[āhé╠P3üi10pin)éÉ┌æ▒   ü@üEæ¬ÆĶÄ×é╔ÄgŚpéĄéĮFPGAé╠ROMāfü[ā^ü@ā_āEāōāŹü[āhé═é▒é┐éń ü@ü@üiSPDIFé®éńāfāWā^āŗāfü[ā^éō³Ś═éĄüAāóā░ī^āmāCāYāVāFü[āsāōāOéŹséóüAD/AāRāōāoü[ā^ā{ü[āhé╠ātāHü[ā}ābāgé┼ÅoŚ═üj ü@üESPDIFé®éńé╠ō³Ś═ÉMŹåātāHü[ā}ābāgé═Æ╩ÅĒātāHü[ā}ābāg24bitŹČŗlé▀ÉĻŚpé╠éĮé▀üASPDIFā{ü[āhé╠SW FMT0/FMT1é═ ü@ü@L / Lé╔āZābāgüB ü@üEFPGAā{ü[āhé╠ÉMŹåéŲSWÉ▌ÆĶé═ł╚ē║é╠Æ╩éĶ  ü@üEFPGAā{ü[āhé╠SWÉ▌ÆĶé═ł╚ē║é╠Æ╩éĶ ü@ü@ć@ō³Ś═āNāŹābāNÉ▌ÆĶü@SW2-SW4üFCK_Sel[2]-CK_Sel[0] ü@ü@ü@L / L / LüFSPDIFā}āXā^ü[āNāŹābāN128süAāTāōāvāŖāōāOāNāŹābāNüiüģ50KHzüj ü@ü@ü@L / L / HüFSPDIFā}āXā^ü[āNāŹābāN128süAāTāōāvāŖāōāOāNāŹābāNüiüģ100KHzüj ü@ü@ü@L / H / LüFSPDIFā}āXā^ü[āNāŹābāN128süAāTāōāvāŖāōāOāNāŹābāNüiüģ200KHzüj ü@ü@ü@H / L / LüFSPDIFā}āXā^ü[āNāŹābāN256süAāTāōāvāŖāōāOāNāŹābāNüiüģ50KHzüj ü@ü@ü@H / L / HüFSPDIFā}āXā^ü[āNāŹābāN256süAāTāōāvāŖāōāOāNāŹābāNüiüģ100KHzüj ü@ü@ü@H / H / LüFSPDIFā}āXā^ü[āNāŹābāN256süAāTāōāvāŖāōāOāNāŹābāNüiüģ200KHzüj ü@ü@ćAValueÉöÉ▌ÆĶü@SW5-SW7üFVL[2]-VL[0] ü@ü@ü@L / L / LüFValueÉöÉ▌ÆĶ0ü@12bit ü@ü@ü@L / L / HüFValueÉöÉ▌ÆĶ1ü@11bit

ü@ü@ü@L / H / LüFValueÉöÉ▌ÆĶ2ü@10bit ü@ü@ü@L / H / HüFValueÉöÉ▌ÆĶ3ü@ 9bit ü@ü@ü@H / L / LüFValueÉöÉ▌ÆĶ4 ü@8bit ü@ü@ü@H / L / HüFValueÉöÉ▌ÆĶ5ü@ 7bit ü@ü@ü@H / H / LüFValueÉöÉ▌ÆĶ6 ü@6bit ü@ü@ü@H / H / HüFValueÉöÉ▌ÆĶ7ü@ 5bit ü@ü@ćBā░āóĤÉöÉ▌ÆĶü@SW8-SW10üFORD[2]-ORD[0] ü@ü@ü@L / L / LüF0Ĥ ü@ü@ü@L / L / HüF1Ĥ ü@ü@ü@L / H / LüF2Ĥ

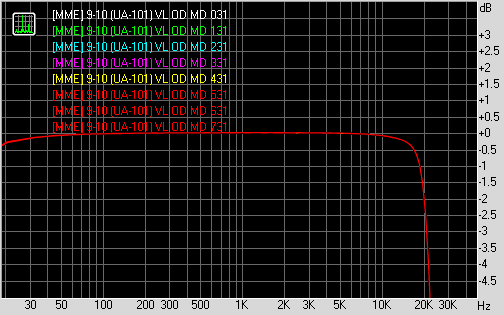

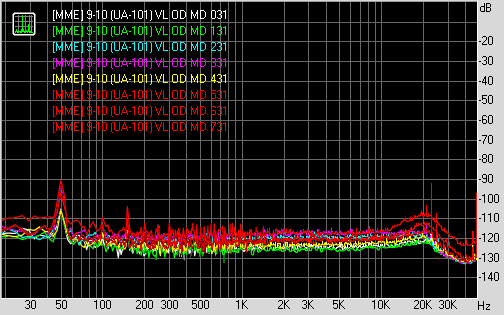

ü@ü@ü@L / H / HüF3Ĥ ü@ü@ü@H / L / LüF4Ĥ ü@ü@ü@H / L / HüF5Ĥ ü@ü@ü@H / H / LüF6Ĥ ü@ü@ü@H / H / HüF7Ĥ ü@ü@ćCō«Źņāéü[āhÉ▌ÆĶü@SW11üFMODE ü@ü@ü@LüFāmāCāYāVāFü[āsāōāOOFFüiPCMāXāŗü[üj ü@ü@ü@HüFāmāCāYāVāFü[āsāōāOON RMAAé╔éµéķæ¬ÆĶīŗē╩ ü@üE3ĤÉöī┼ÆĶüAValueÉööõŖrüi5bitü`12bitüjæ¬ÆĶīŗē╩ Testing chain: External loopback (line-out - line-in)

|

| Test | [MME] 9-10 (UA-101) VLOD MD031 | [MME] 9-10 (UA-101) VLOD MD131 | [MME] 9-10 (UA-101) VLOD MD231 | [MME] 9-10 (UA-101) VLOD MD331 | [MME] 9-10 (UA-101) VLOD MD431 | [MME] 9-10 (UA-101) VLOD MD531 | [MME] 9-10 (UA-101) VLOD MD631 | [MME] 9-10 (UA-101) VLOD MD731 |

| Frequencyresponse(from 40 Hzto 15 kHz), dB: | +0.05, -0.38 | +0.05, -0.39 | +0.05, -0.39 | +0.05, -0.39 | +0.05, -0.39 | +0.05, -0.38 | +0.05, -0.39 | +0.05, -0.39 |

| Noise level,dB (A): | -91.6 | -91.8 | -86.0 | -85.8 | -90.0 | -89.1 | -85.0 | -83.0 |

| Dynamicrange, dB (A): | 90.7 | 89.5 | 87.9 | 86.6 | 85.6 | 87.4 | 86.6 | 79.1 |

| THD, %: | 0.031 | 0.029 | 0.029 | 0.029 | 0.029 | 0.034 | 0.032 | 0.058 |

| IMD +Noise, %: | 0.038 | 0.036 | 0.036 | 0.037 | 0.037 | 0.040 | 0.044 | 0.076 |

| Stereocrosstalk, dB: | -90.9 | -92.6 | -86.1 | -89.1 | -86.9 | -88.9 | -86.5 | -80.7 |

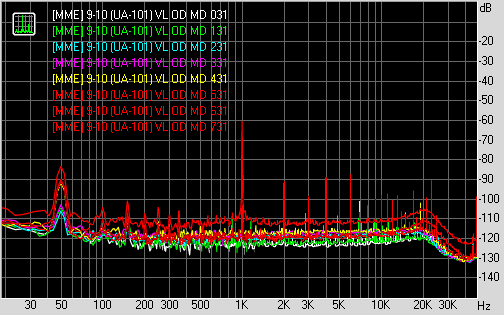

Frequency response

Noise level

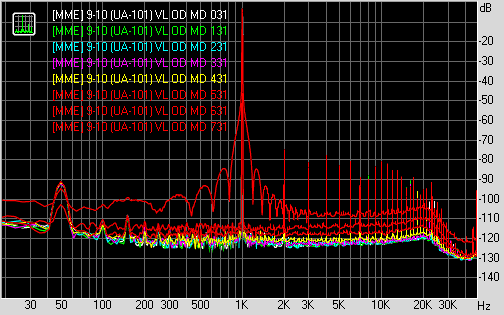

Dynamic range

THD + Noise (at -3 dB FS)

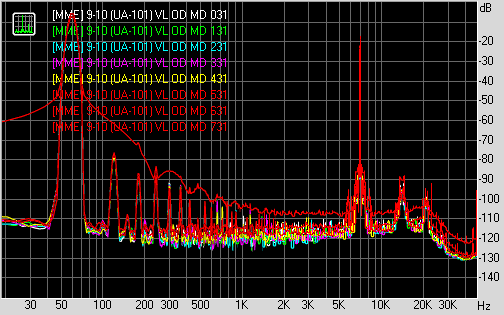

Intermodulation distortion

Stereo crosstalk

Testing chain: External loopback (line-out - line-in)

Sampling mode: 24-bit, 96 kHz

Summary

| Test | [MME] 9-10(UA-101)VL OD MD411 | [MME] 9-10(UA-101)VL OD MD421 | [MME] 9-10(UA-101)VL OD MD431 | [MME] 9-10(UA-101)VL OD MD441 | [MME] 9-10(UA-101)VL OD MD451 |

| Frequencyresponse (from40 Hz to 15 kHz),dB: | +0.05, -0.38 | +0.05, -0.38 | +0.05, -0.39 | +0.05, -0.39 | +0.05, -0.39 |

| Noise level, dB(A): | -96.2 | -95.7 | -90.0 | -89.0 | -89.5 |

| Dynamic range,dB (A): | 78.5 | 83.7 | 85.6 | 88.2 | 89.5 |

| THD, %: | 0.038 | 0.029 | 0.029 | 0.030 | 0.032 |

| IMD + Noise, %: | 0.050 | 0.038 | 0.037 | 0.037 | 0.039 |

| Stereo crosstalk,dB: | -92.6 | -91.9 | -86.9 | -88.0 | -87.7 |

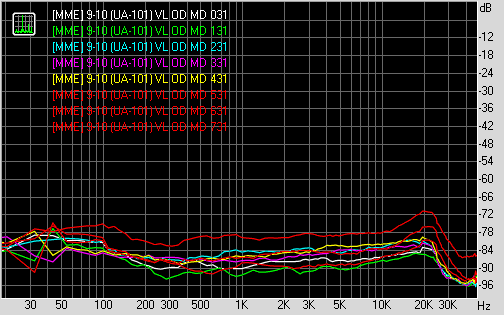

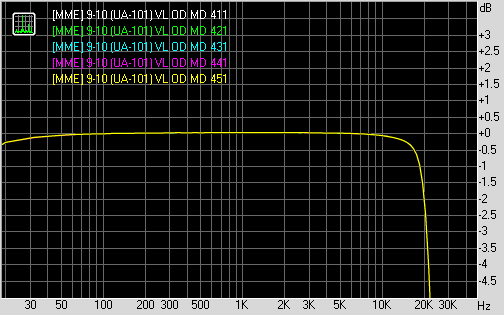

Frequency response

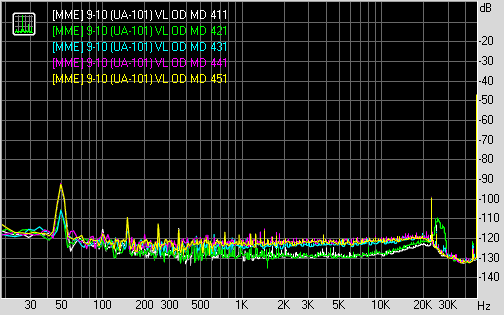

Noise level

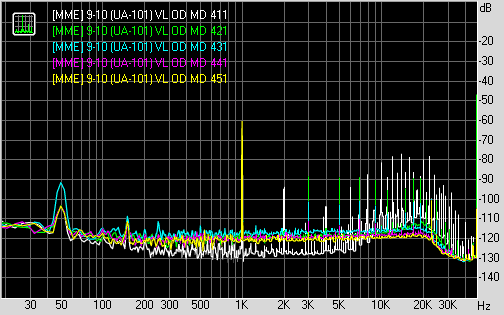

Dynamic range

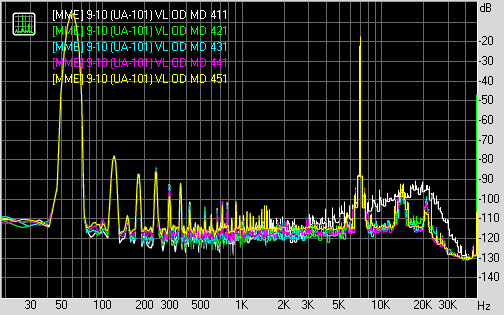

THD + Noise (at -3 dB FS)

Intermodulation distortion

Stereo crosstalk

| üb āvāēāCāoāVü[ā|āŖāVü[ü@übü@ō┴ÆĶÅżÄµł°¢@é╔ŖŅé├éŁĢ\Ä”ü@übü@ēcŗŲō·āJāīāōā_ü[ü@übü@æŚŚ┐ü@üb é©¢ŌéóŹćé╣ üb ē’ÄąŖTŚv üb Copyright (C) 2015-2020 Realize Technology Corporation All Rights Reserved. |