■R-2R(抵抗ラダー)方式 D/Aコンバータの実用化に向けた技術開発(1)

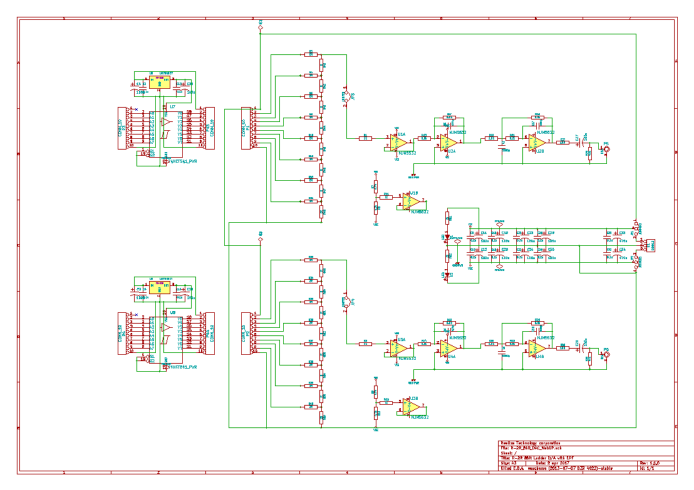

| ◆2017/04/02 R-2R(抵抗ラダー)方式のD/Aコンバータを使用して、実用レベルの性能を引き出す事を目指します。 準備したのは、8bitのR-2R方式D/Aコンバータ 回路図は以下ですが、詳細はこちらからダウンロードしてください。  R-2Rの出力はボルテージフォロワーで受けた後、LPFを通して出力する構成です。 前段(ロジックとのI/F部)にHC541によるレベルシフタを設けてあります。 R-2R方式のD/Aコンバータを8bitとした理由は、以下の2点です。 ①RTA-μPD6376(D/Aコンバータボード)の高性能駆動のページでご紹介したとおり、129値出力での実績がある。

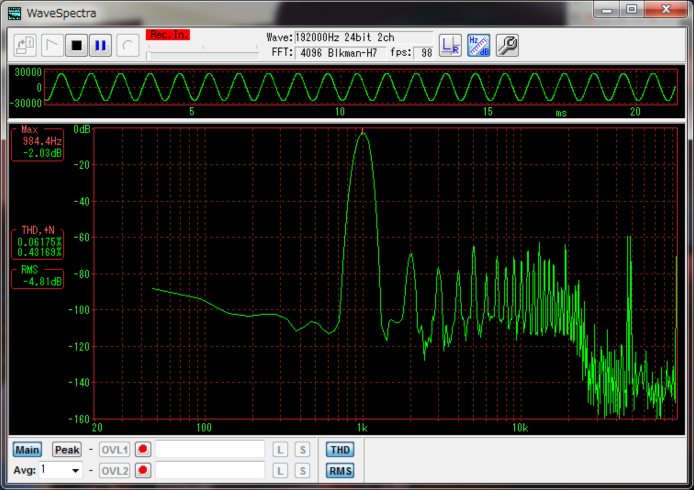

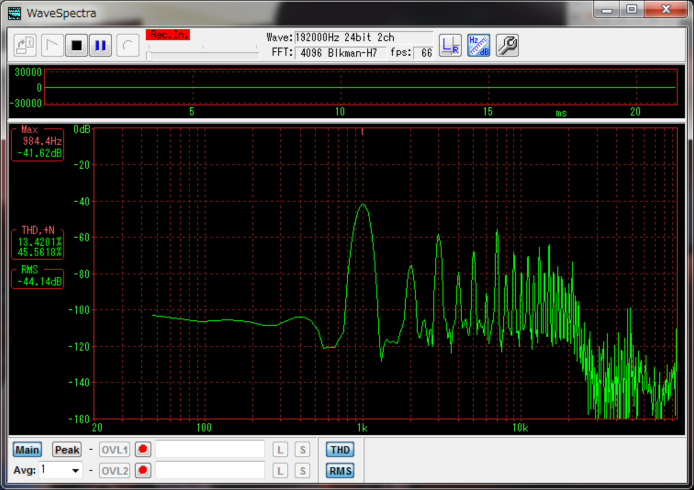

②R-2RのD/Aコンバータを駆動する論理回路の規模とI/O数から。(いずれも使用するFPGAの制約より) ※I/O数が多く、インプリできる回路規模の大きいFPGAを使用する場合は、R-2Rのbit数を増やすことが可能です。 ◆2017/04/03 8bit R-2Rの出力特性(Lchのみ掲載) 動作は、16bit PCMデータの上位8bitの符号bitのみ反転し、ストレートバイナリ化して、駆動 <Sin1KHz 0dB入力 Lch>  <Sin1KHz -20dB入力 Lch>  <Sin1KHz -40dB入力 Lch>  <Sin1KHz -60dB入力 Lch>  <Sin1KHz -80dB入力 Lch>  ☆歪成分もさることながら、-40dBあたりから、レベルが非線形になっています。 |

| | プライバシーポリシー | 特定商取引法に基づく表示 | 営業日カレンダー | 送料 | お問い合せ | 会社概要 | Copyright (C) 2015-2020 Realize Technology Corporation All Rights Reserved. |